東芝メモリが開発し、製造しているのは、NANDフラッシュという半導体メモリである。そのNANDは、2次元の微細化が困難になったため、3次元化することになった。そして、3次元NAND市場が爆発しつつある。連載第2回目では、NANDが3次元化する理由を述べた後、その3次元NAND市場が爆発的に拡大しつつある実態を説明する。

なぜ2次元ではなく3次元か

半導体には、「2年で集積度が2倍になる」というムーアの法則がある。その際、素子の大きさが変わらなければ、チップが大きくなってしまうので、2年で2倍高集積化する際には、「2年で0.7倍微細化する」ことが必要になる。なぜ0.7倍かというと、0.7×0.7=0.49、つまり、素子の面積を半分にするということである。

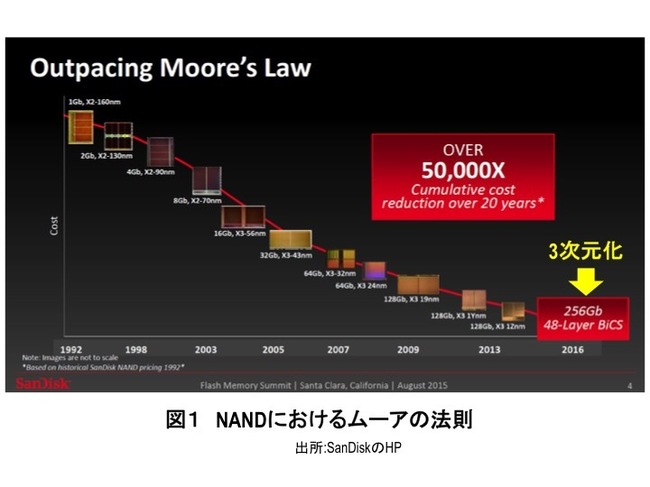

では、NANDにおけるムーアの法則を見てみよう(図1)。1992年に160nmで1G(ギガ、10億)ビットだったNANDは、その後、130nmで2Gビット、90nmで4Gビット、70nmで8Gビット、56nmで16Gビット、43nmで32Gビット、32nmで64Gビット、24nmで64Gビット(チップシュリンク)、19nmで128Gビットと、微細化と高集積化、チップシュリンクを推進してきた。

ところが、128Gビットに到達した後、チップ面積を縮小するために、19nm(1X)→1Y→1Zと微細化し、16~15nmまで来たところで、大きな壁に直面した。

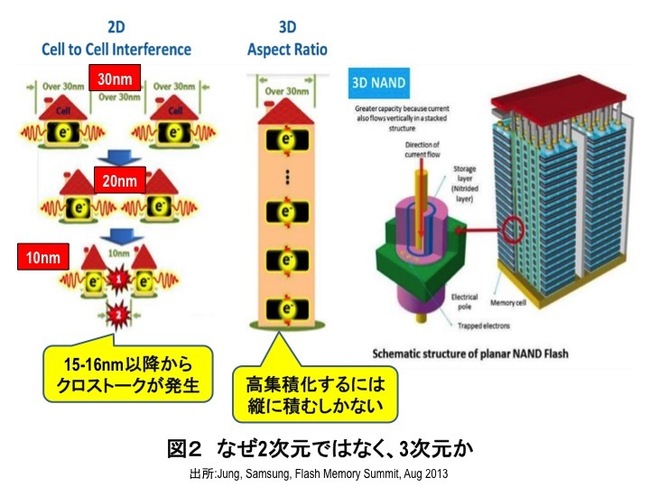

16~15nm以降も微細化は可能なのだが、それ以上微細化してメモリセルが接近し過ぎると、隣り合うメモリセル同士が干渉し合う(クロストーク)という問題が起き始めたのである(図2)。

クロストークを避けるためには、メモリセル間に一定の距離が必要である。しかし、メモリセル間を詰めることなく、セルを微細化したり、チップを高集積化するのはほぼ不可能である。そこで考え出されたのが、セルを縦に積む方式、つまり3次元NANDである。

3次元NANDでは、高集積化のために、メモリセルは微細化せず、その代りに縦方向に何層積層するかという競争をしている。4~5年ほど前から始まった3次元NANDの開発は、8~16層を経て24層から32層に移行し、2016年3月に先陣を切って、サムスン電子の西安工場(中国)が48層で大量生産を開始した。東芝は半年~1年遅れとなっている。そして現在の最先端は64層であり、ここでもサムスン電子が先行している。