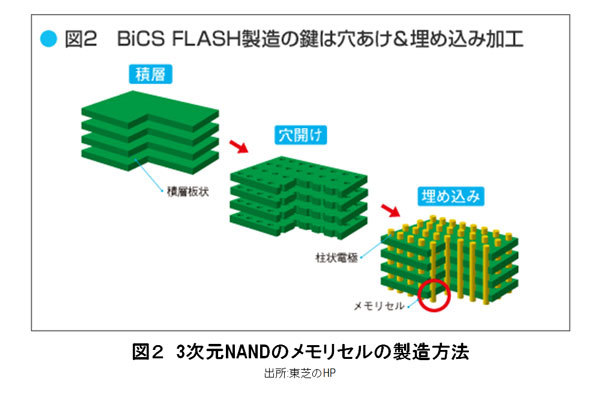

3次元NANDのメモリセルのつくり方

この高層マンションのような3次元NANDのメモリセルはどうやってつくるのか。東芝のHPに簡単な製造方法が書いてあるので、これを元に説明する(図2)。

例えば48層の3次元NANDをつくる場合、まず、シリコン酸化膜(SiO2)などの絶縁膜を48層積層する。次に、48層積層された膜を縦に貫通する微細な孔を形成する。最後に、この孔をタングステン(W)などの金属で埋め込む。本当はもっと複雑なのだが、本稿では深入りせずに、「膜を積んで、孔をあけて、金属で埋め込む」程度にとどめておく。

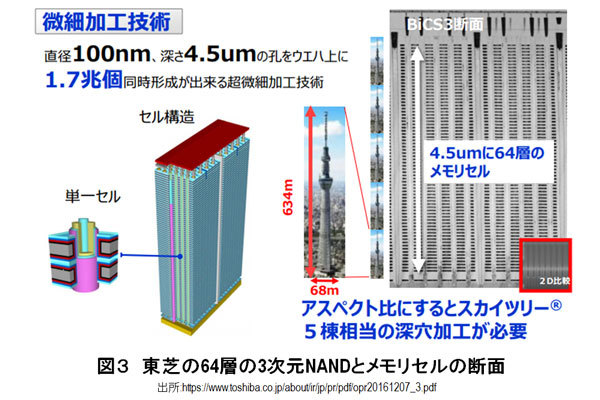

最も難しいのは深孔加工

この中で特に難しいのが、ドライエッチングと呼ばれる技術を使って、微細で深い孔をあける工程である。東芝のIR資料の中に、その難しさを直感的に理解するのにちょうど良い図があったのでそれを基に説明しよう(図3)。これは、東芝の64層の3次元NANDの模式図(左側)と断面顕微鏡写真(右側)を示している。

右側の写真のように縦方向に64層のメモリセルを形成するには、直径100nmで深さ4.5μm(4500nm)の孔を開けなければならない。孔の深さと直径の比をアスペクト比と呼んでいるが、この3次元NANDでは、アスペクト比45:1の孔をあける必要があるわけだ。この孔のアスペクト比は、高さ634mで底辺68mの東京スカイツリー5棟分に相当すると東芝は説明している。そして、このような超高アスペクト比の孔を12インチウエハ上に1兆7000億個も同時に開けなければならないのである。

かつて筆者は日立やエルピーダで、DRAMというNANDとはちょっとタイプの違う半導体メモリのドライエッチングを担当していた。2000年頃に、当時最先端だった64MビットDRAMのキャパシタ用の深孔を「もう限界だ、もう無理だ」とヒイヒイ言いながら加工していたことを記憶しているが、そのアスペクト比は、たったの12:1だった。

そして現在、最先端のDRAMは4Gビットであるが、そのキャパシタ用の深孔のアスペクト比はせいぜい20~25程度である。DRAMでは、この深孔の加工が非常に難しいため、微細化がスローダウンしており、半導体デバイスの中ではもっとも早く微細化の終焉が来ると言われているほどである。

ところが、3次元NANDでは、アスペクト比45:1の孔を開けなければならないのである。しかも、今後、積層数が増大するため、より深い孔をあける必要に迫られており、そのアスペクト比は60:1~80:1になりつつある。

アスペクト比12:1の孔をあけるのに苦労していた筆者としては、正直なところ、「3次元NANDの深孔加工担当のドライエッチング技術者でなくてよかった」と思うほどである。東芝もサムスン電子もマイクロンもSK Hynixも、3次元NANDの深孔加工担当者には、同情を禁じ得ない。