3次元NANDで周回遅れとなった東芝

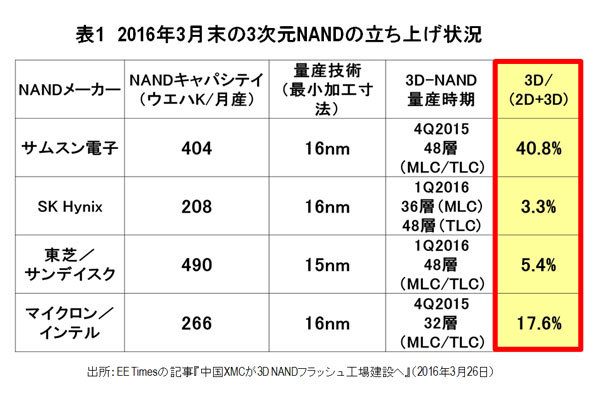

米半導体業界誌EE Timesの2016年3月26日の記事に、世界に4グループあるNANDメーカーにおける3次元NANDの立ち上げ状況を示すデータが掲載された(表1)。それは、衝撃的だった。

表1によれば、サムスン電子のNANDの生産キャパシティは月産ウエハ枚数40.4万枚で、2015年第4四半期に48層の3次元NANDの量産を開始し、2016年3月時点では全キャパ内の40.8%で3次元NANDを生産していることになる。

一方、東芝&サンディスクは、2016年第1四半期から48層の3次元NANDの生産を開始しているが、月産49万枚のキャパの内、3次元NANDに使われているのは、たった5.4%しかない。これは、SK Hynixの3.3%よりましだが、マイクロン&インテルの17.6%の1/3以下である。

NANDは1987年に東芝が発明した半導体メモリであり、2007年に世界に先駆けて3次元NANDの学会発表を行ったのも東芝である。にもかかわらず、なぜ、その量産でサムスン電子にこれほどまで差をつけられてしまったのか。

本稿では、その第1の原因が3次元NANDの途轍もなく難しい深孔加工技術にあったことを述べる。また、第2の原因として、サムスン電子が3次元NAND工場を中国の西安に建設したことも影響していることを論じる。

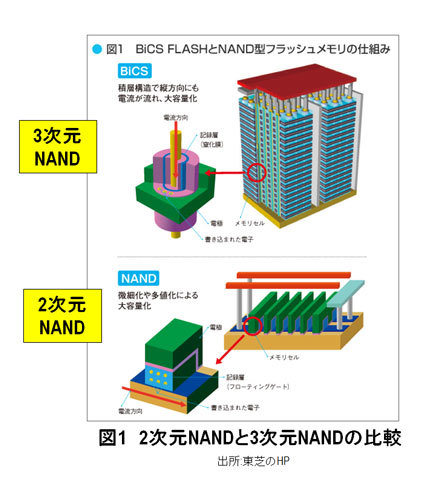

2次元NANDと3次元NANDの比較

第2回のコラムで、2次元NANDを微細化していくと、15~16nm付近からメモリセル同士の干渉(クロストーク)が起きるため、メモリセルを縦方向に積む3次元化が考案されたと説明した。

東芝のHPに掲載されている2次元と3次元(BiCS)の比較図を見てみよう(図1)。尚、BiCSとは、Bit Cost Scalableの略で、東芝の3次元NANDの呼称である(一方、サムスン電子は、Vertical-NAND(V-NAND)と呼称している)。

2次元が江戸時代に存在した庶民用住居の“長屋”のような構造であるのに対し、3次元は超高層マンションのような構造となっていることがわかる。前節で「サムスン電子が48層の3次元NANDを量産開始」とかいたが、この「48層」とは、縦方向にメモリセルが48個積層していることを意味する。要するに、48階建てのマンションと思って頂ければいいだろう。そして、積層数が高いほど、単位面積辺りのメモリセル密度が大きくなるため、NANDメーカーは、どれだけ積層できるかという競争をしているわけだ。